5、environment类和testcase类的创建及仿真

...大约 2 分钟

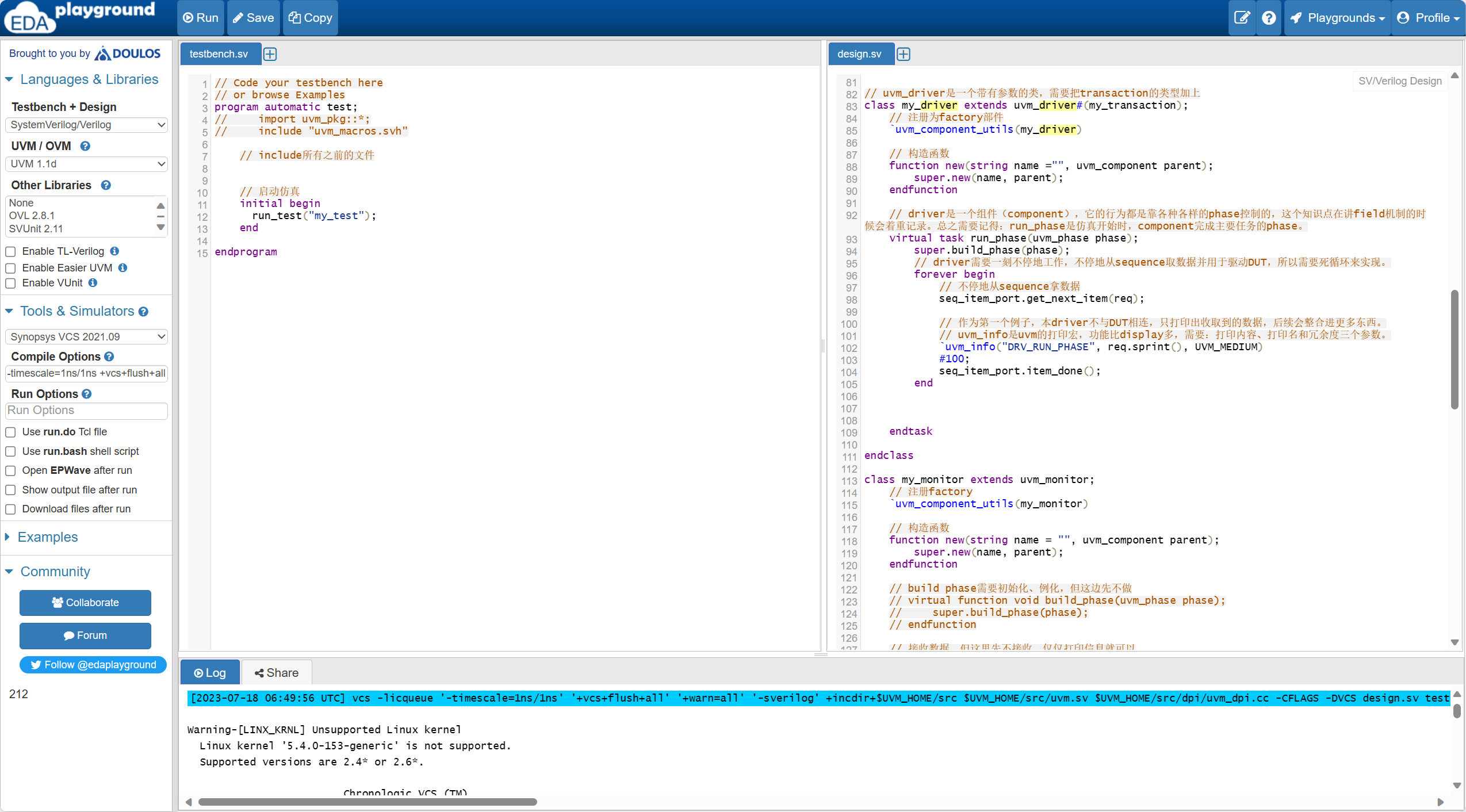

environment是几乎涵盖所有验证平台核心组件的容器类,主要任务是配置一部分平台组件,并把它们实例化。testcase是包围environment的一个组件,目的是选择启动的sequence类型,以及完成一些配置。最后,需要在program块中启动仿真。==本章章内相关位置及末尾会给出查看示例代码的网站,文章末尾的网站仅为汇总。注意,这些示例代码可能会和内容展示的代码不太一样,因为这些代码是在这章写完后才编写的。代码内容仅供参考,可以随意转载,转载请带上作者博客链接。这些代码存在于EDAPlayground中。如果需要在线运行,需要注册。==

EDAplayground

部分仿真结果

5、environment类和testcase类的创建及仿真

5.1 environment

class my_env extends uvm_env;

`uvm_component_utils(my_env)

// 需要例化的模块,在这里声明

// 因为没有和DUT的交互,所以现在只声明例化master agent

my_agent i_agent;

function new(string name="", uvm_component parent);

super.new(name, parent);

endfunction

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

i_agent = my_agent::type_id::create("i_agent", this);

endfunction

endclass

5.2 testcase

class my_test extends uvm_test;

`uvm_component_utils(my_test)

my_env m_env;

function new(string name = "", uvm_component parent);

super.new(name, parent);

endfunction

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

m_env = my_env::type_id::create("m_env", this);

// 选择需要启动的sequence,用config机制完成

uvm_config_db#(uvm_object_wrapper)::set(

this, "*.m_seqr.run_phase", "default_sequence", my_sequence::get_type()

);

endfunction

// 可选项,打印整个验证平台的结构

virtual function void start_of_simulation_phase(uvm_phase phase);

super.start_of_simulation_phase(phase);

uvm_top.print_topology(uvm_default_tree_printer);

endfunction

endclass

5.3 仿真

仿真首先需要创建一个program块。因为不涉及到interface,所以program块是可行的。如果需要用interface的话,还是得用module才行。

program automatic test;

import uvm_pkg::*;

include "uvm_macros.svh"

// include所有之前的文件

// 启动仿真

initial begin

run_test();

end

endprogram

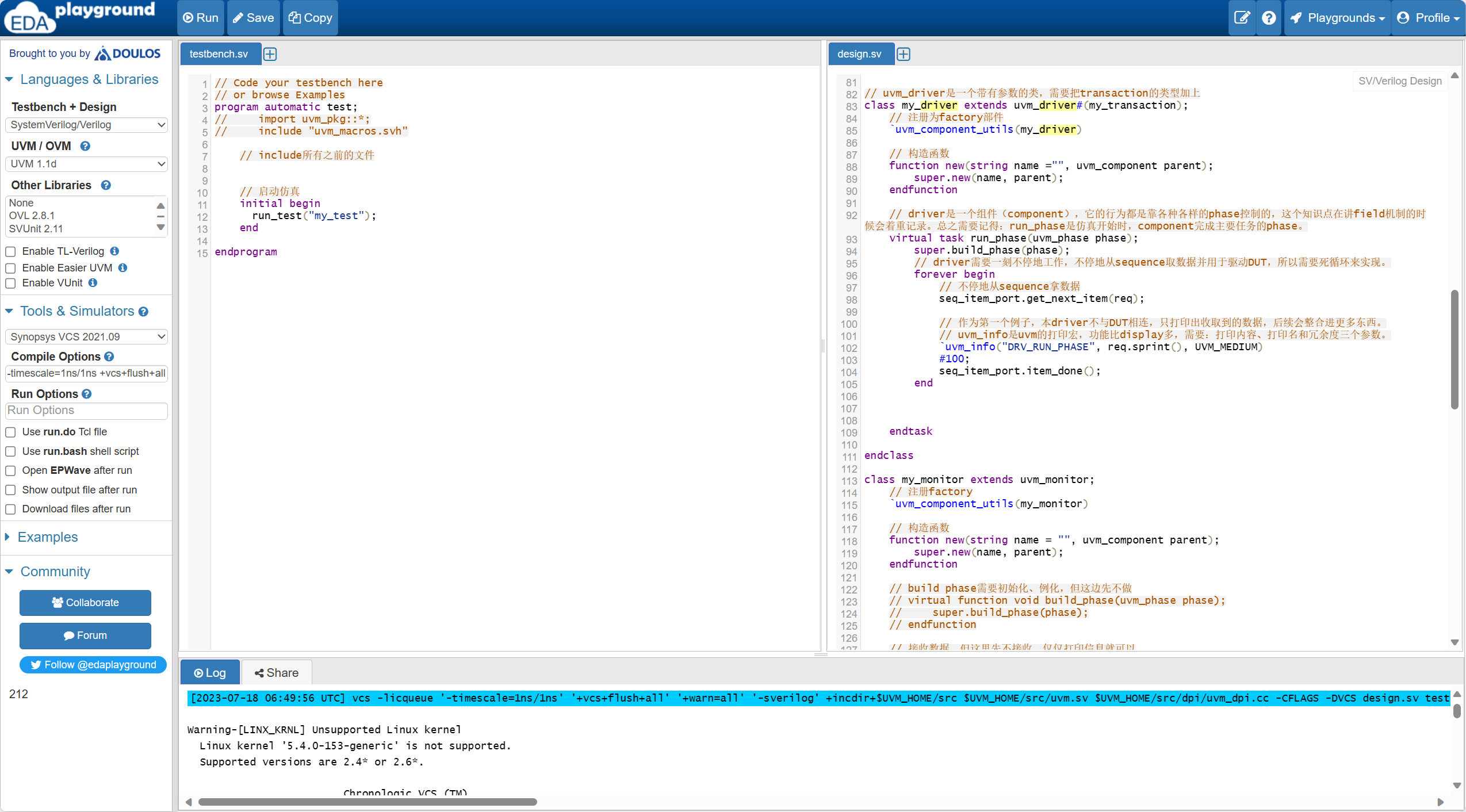

接下来,把前面每一段代码都按顺序复制粘贴到我在用的在线EDA工具EDAplayground里面:

在左边选择UVM 1.1d,然后选择VCS作为仿真器,这里用的是VCS 2021。然后点击保存,把左边show output file after run点掉,再点run就可以成功运行了!

不过需要注意:

- 这个平台会自动导入uvm_pkg和uvm_macros.svh,所以可以注释掉。

- 这个平台在启动仿真的run_test语句中需要填入启动的仿真testcase,这个testcase必须是一个component(我这里就是),所以可以把run_test()改成run_test("my_test")

这样就可以正常仿真出结果了。

可以看到它的仿真命令:

vcs -licqueue '-timescale=1ns/1ns' '+vcs+flush+all' '+warn=all' '-sverilog' +incdir+$UVM_HOME/src $UVM_HOME/src/uvm.sv $UVM_HOME/src/dpi/uvm_dpi.cc -CFLAGS -DVCS design.sv testbench.sv && ./simv +vcs+lic+wait

这个以后会学到。

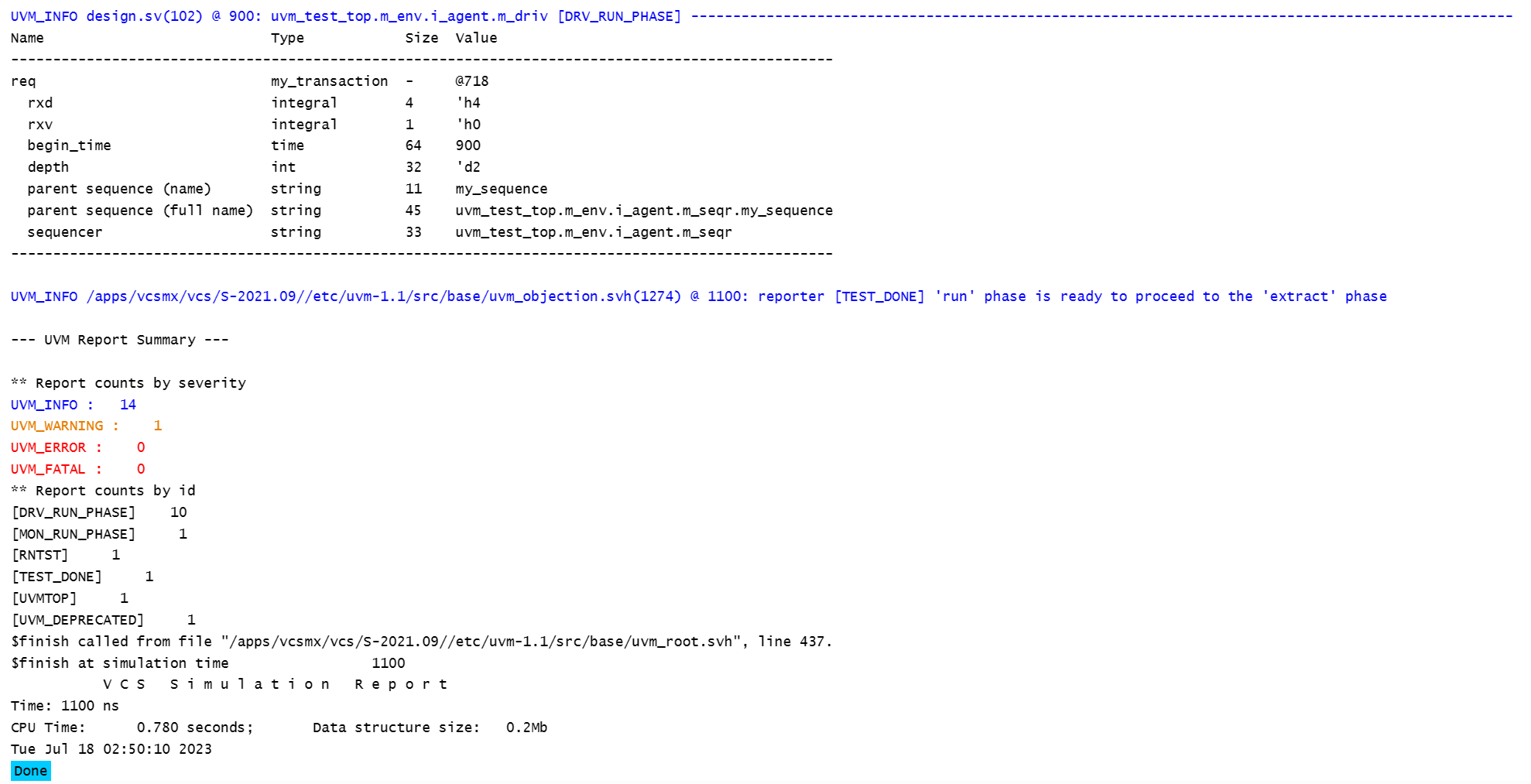

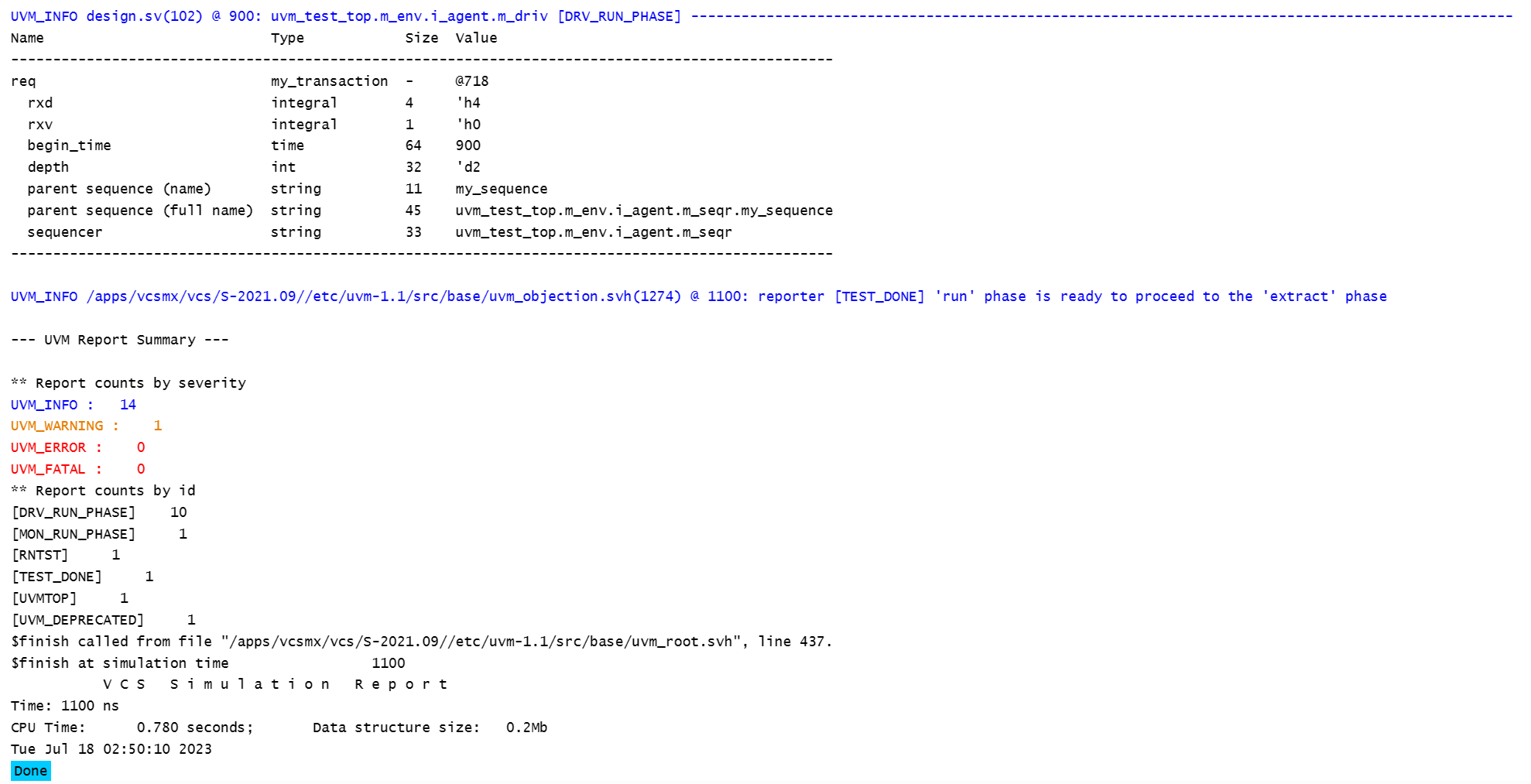

仿真结果:

这样就仿真完毕。

示例代码

Powered by Waline v2.15.5